以VHDL格式生成2个时钟脉冲

虽然我已经完成了数字逻辑大学课程,但我是VHDL设计的新手,我希望有人可以帮我创建2个时钟信号,这些信号取决于彼此的状态。

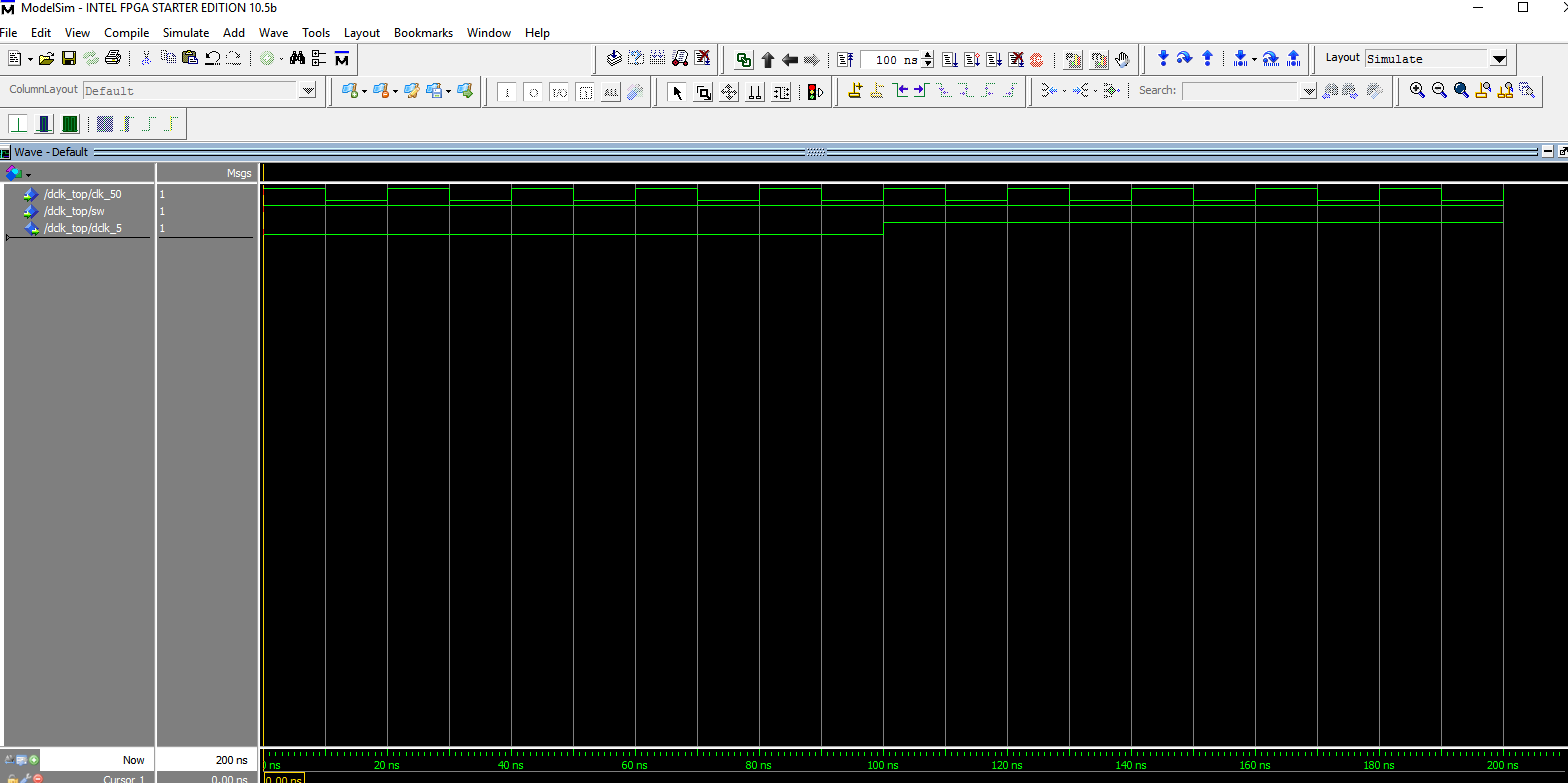

我在DE2-115 FPGA板上使用50 MHz时钟,用于创建5MHz时钟(名为dclk_5)。但是,模拟显示两个信号,但运行时间仅为200 ns,不再运行。为什么模拟运行的时间不超过200 ns?

2个时钟的数据表:

用于测试dclk_5和clk_50的替代VHDL设计合成但模拟不正确:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity DCLK_top is

port(

clk_50 : in std_logic;

sw : in std_logic;

dclk_5 : out std_logic

);

end DCLK_top;

architecture behaviour of DCLK_top is

signal clk_counter : integer range 0 to 10 := 0;

signal dclk_counter : integer range 0 to 8 := 0;

signal dclk_pause_counter : integer range 0 to 7 := 0;

signal dclk_pause : std_logic := '0';

signal clk_pause_counter : integer range 0 to 7 := 0;

begin

dclk_proc : process(clk_50)

begin

if(clk_50'event and clk_50='1' ) then

clk_counter <= clk_counter+1;

if(clk_counter=10) then

clk_counter <= 0;

end if;

if(clk_counter<5) then

dclk_5 <= '0';

else

dclk_5 <= '1';

end if;

end if;

end process dclk_proc;

end architecture behaviour;

模拟图片:

1 个答案:

答案 0 :(得分:1)

嗯,你的代码并没有那么糟糕,但有一个问题。

clk_counter <= clk_counter+1;

if(clk_counter=10) then

clk_counter <= 0;

end if;

因此,直到流程结束才会分配<=分配。所以clk_counter在整个过程中都是9。它将被设置为10,但直到进程结束,因此if语句不会触发。

所以下一次评估过程,clk_counter是10.现在是if语句/将/触发器。但是,在此之前你要为clk_counter分配10 + 1 = 11.但是这是不允许的,因为clk_counter的范围是0到10.你可以将范围设置为11,这不会发生。但是代码没有做你想做的事情。

所以,更清洁的代码是更好的imho。 E.g:

if(clk_counter<10) then

clk_counter <= clk_counter+1;

else

clk_counter <= 0;

end if;

您还可以将dclk的分配与流程分开。 E.g:

dclk <= '0' when (clk_counter<5) else '1';

但这不是小故障。你最好为你的任务计时,就像你已经在做的那样。

相关问题

最新问题

- 我写了这段代码,但我无法理解我的错误

- 我无法从一个代码实例的列表中删除 None 值,但我可以在另一个实例中。为什么它适用于一个细分市场而不适用于另一个细分市场?

- 是否有可能使 loadstring 不可能等于打印?卢阿

- java中的random.expovariate()

- Appscript 通过会议在 Google 日历中发送电子邮件和创建活动

- 为什么我的 Onclick 箭头功能在 React 中不起作用?

- 在此代码中是否有使用“this”的替代方法?

- 在 SQL Server 和 PostgreSQL 上查询,我如何从第一个表获得第二个表的可视化

- 每千个数字得到

- 更新了城市边界 KML 文件的来源?