VHDL FSMи®ҫзҪ®еҚ•е…ғиҫ“е…Ҙ并дҪҝз”ЁзӣёеҗҢзҠ¶жҖҒзҡ„иҫ“еҮә

жҲ‘жӯЈеңЁvhdlдёӯе®һзҺ°Mealyзұ»еһӢзҡ„FSMгҖӮжҲ‘зӣ®еүҚжӯЈеңЁдҪҝз”ЁеҸҢйҮҚиҝҮзЁӢпјҢиҷҪ然жҲ‘еҲҡиҜ»иҝҮеҚ•дёӘиҝҮзЁӢеҸҜиғҪжӣҙж•ҙжҙҒгҖӮиҖғиҷ‘дёҖдёӢдҪ зӯ”жЎҲзҡ„еҸӮж•°гҖӮ

й—®йўҳзҡ„з®ҖзҹӯзүҲжң¬жҳҜпјҡжҲ‘еҸҜд»ҘжңүдёҖдёӘзҠ¶жҖҒпјҢе…¶дёӯеҸҰдёҖдёӘ组件зҡ„иҫ“е…Ҙиў«жӣҙж”№пјҢ并且пјҢеңЁзӣёеҗҢзҡ„зҠ¶жҖҒдёӢпјҢдҪҝз”ЁжүҖиҝ°з»„件зҡ„иҫ“еҮәпјҹиҝҷжҳҜе®үе…ЁиҝҳжҳҜз«һдәүжҝҖзғҲпјҹжҲ‘еә”иҜҘдҪҝ用组件зҡ„иҫ“еҮәеҲӣе»әеҸҰдёҖдёӘзҠ¶жҖҒпјҹ

й•ҝзүҲпјҡжҲ‘жңүдёҖдёӘеҶ…еӯҳжЁЎеқ—гҖӮиҝҷжҳҜдёҖдёӘfifoеҶ…еӯҳпјҢжҝҖжҙ»е…¶еӨҚдҪҚдҝЎеҸ·дјҡе°ҶеҗҚдёәqueue_pointerзҡ„еҸҳйҮҸеёҰеҲ°е…¶з¬¬дёҖдёӘе…ғзҙ гҖӮеҶҷе…ҘеӯҳеӮЁеҷЁеҗҺпјҢжҢҮй’ҲдјҡеўһеҠ пјҢеҰӮжһңи¶…еҮәиҢғеӣҙпјҢе®ғпјҲ然еҗҺд№ҹпјүеӨҚдҪҚеҲ°з¬¬дёҖдёӘе…ғзҙ пјҢ并且иҫ“еҮәдҝЎеҸ· done иў«жҝҖжҙ»гҖӮйЎәдҫҝиҜҙдёҖдёӢпјҢжҲ‘е°ҶиҝҷдёӘ组件称дёәFIMEMгҖӮ

жҲ‘зҡ„FSMйҰ–е…Ҳзј–еҶҷж•ҙдёӘFIMEMпјҢ然еҗҺиҪ¬еҗ‘е…¶д»–дәӢйЎ№гҖӮжңҖеҗҺдёҖж¬ЎеҶҷдҪңе°Ҷд»Һе·һе®ҢжҲҗпјҡ

when SRAM_read =>

READ_ACK <= '1';

FIMEM_enable <= '1';

FIMEM_write_readNEG <= '0';

if(FIMEM_done = '1') then --is that too fast? if so, we're gonna have to add another state

FIMEM_reset <= '1'; --this is even faster, will need check

data_pipe_to_FOMEM := DELAYS_FIMEM_TO_FOMEM;

next_state <= processing_phase1;

else

SRAM_address := SRAM_address + 1;

next_state <= SRAM_wait_read;

end if;

еңЁжӯӨзҠ¶жҖҒдёӢпјҢеҗҜз”Ёе’ҢеҶҷе…Ҙжҙ»еҠЁж„Ҹе‘ізқҖж•°жҚ®е°ҶеҶҷе…ҘFIMEMгҖӮеҰӮжһңиҝҷжҳҜеҶ…еӯҳдёӯзҡ„жңҖеҗҺдёҖдёӘж•°жҚ®з©әй—ҙпјҢFIMEM_doneе°ҶжҝҖжҙ»пјҢifдёӯзҡ„еӨ§еқ—д»Јз Ғе°ҶеӨ„зҗҶжңӘжқҘгҖӮдҪҶжҳҜпјҢиҝҳжңүи¶іеӨҹзҡ„ж—¶й—ҙеҗ—пјҹеҰӮжһңжІЎжңүпјҢ并且дёӢдёҖдёӘзҠ¶жҖҒиҝӣе…ҘSRAM_wait_readпјҢ然еҗҺFIMEM_doneиў«жҝҖжҙ»пјҢеҲҷдјҡеҮәзҺ°й—®йўҳгҖӮдәӢе®һдёҠFIMEMжҳҜе®Ңе…ЁеҗҢжӯҘзҡ„пјҲиҷҪ然жҲ‘зҡ„д»Јз Ғзҡ„иҝҷйғЁеҲҶжҳҜеңЁејӮжӯҘиҝҮзЁӢдёӯпјүдјҡжӣҙеҠ ж··д№ұеҗ—пјҹ

иҝҷжҳҜжҲ‘зҡ„и®°еҝҶд»Јз ҒпјҢд»ҘйҳІдёҮдёҖпјҡ

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity memory is

generic (size: positive := 20);

Port ( clk,

reset,

enable,

write_readNEG: in std_logic;

done: out std_logic;

data_in: in STD_LOGIC_VECTOR(7 downto 0);

data_out: out STD_LOGIC_VECTOR(7 downto 0) );

end memory;

architecture Behavioral of memory is

subtype word is STD_LOGIC_VECTOR(7 downto 0);

type fifo_memory_t is array (0 to size-1) of word;

signal fifo_memory : fifo_memory_t :=((others=> (others=>'0')));

--Functionality instructions:

--Resetting sets the queue pointer to the first element, and done to 0

--Each cycle with enable active, a datum from the pointer position is

--written/read according to write_readNEG, and the pointer is incremented.

--If the operation was at the last element, the pointer returns to the first place

--and done is set to 1. When done is 1, enable is ignored.

Begin

process(clk,reset)

variable done_buf : std_logic;

variable queue_pointer: natural range 0 to size-1;

begin

if(reset = '1') then

queue_pointer := 0;

done_buf := '0';

elsif(rising_edge(clk)) then

if(done_buf = '0' and enable = '1') then

case write_readNEG is

when '0' =>

data_out <= fifo_memory(queue_pointer);

when '1' =>

fifo_memory(queue_pointer) <= data_in;

when others => null;

end case;

if(queue_pointer = size-1) then

done_buf := '1';

queue_pointer := 0;--check

else

queue_pointer := queue_pointer + 1;

end if;

end if; --enable x not done if

end if; --reset/rising edge end if

done <= done_buf;

end process;

End Behavioral;

第дёҖжқЎиҜ„и®әеҗҜеҸ‘дәҶжӣҙеӨҡз»ҶиҠӮпјҡ

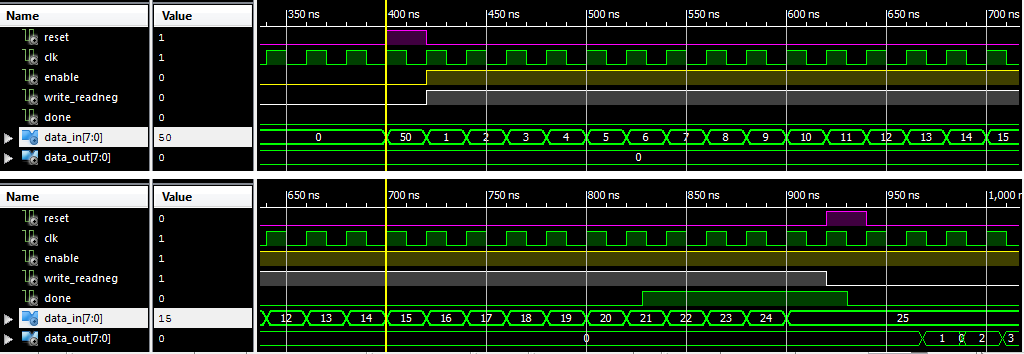

еҶ…еӯҳеҸҜд»ҘеңЁжҝҖжҙ»зӣёеҗҢе‘ЁжңҹеҗҜз”Ёж—¶иҜ»еҸ–ж•°жҚ®пјҢеҰӮдёӢжүҖзӨәпјҡ жіЁж„ҸвҖң1вҖқпјҲеҗҜз”Ёж—¶зҡ„еҖјиў«жҝҖжҙ»пјүе®һйҷ…дёҠжҳҜеҰӮдҪ•еҶҷе…ҘеҶ…еӯҳзҡ„гҖӮ

жіЁж„ҸвҖң1вҖқпјҲеҗҜз”Ёж—¶зҡ„еҖјиў«жҝҖжҙ»пјүе®һйҷ…дёҠжҳҜеҰӮдҪ•еҶҷе…ҘеҶ…еӯҳзҡ„гҖӮ

дёҚе№ёзҡ„жҳҜпјҢиҝҷж®өд»Јз ҒжҳҜеңЁејӮжӯҘиҝҮзЁӢдёӯпјҒиҷҪ然жҲ‘йқһеёёејәзғҲең°жғіиҰҒиҪ¬еҗ‘еҚ•дёҖиҝҮзЁӢжҸҸиҝ°гҖӮ

дёҺжҲ‘иҝ„д»Ҡдёәжӯўи®ҫи®Ўзҡ„жүҖжңүз”өи·ҜзӣёжҜ”пјҢжҲ‘еҫҲйҡҫйҖҡиҝҮд»ҝзңҹжөӢиҜ•е®ғгҖӮиҝҷжҳҜжҲ‘еӨ§еӯҰзҡ„дёҖдёӘйЎ№зӣ®пјҢжҲ‘们е°ҶvhdlзЁӢеәҸдёӢиҪҪеҲ°xilinx spartan 3 FPGAгҖӮиҝҷдёҖж¬ЎпјҢжҲ‘们еҫ—еҲ°дәҶдёҖдёӘеңЁMatlabе’ҢFPGAзҡ„SRAMд№Ӣй—ҙдј иҫ“ж•°жҚ®зҡ„еҚ•е…ғпјҲе…¶еҠҹиғҪпјҢжҲ‘дёҚзҹҘйҒ“пјүгҖӮеӣ жӯӨпјҢжҲ‘еҝ…йЎ»дҪҝз”ЁжӯӨеҚ•е…ғеңЁSRAMе’ҢжҲ‘зҡ„еҶ…еӯҳжЁЎеқ—д№Ӣй—ҙдј иҫ“ж•°жҚ®гҖӮиҝҷж„Ҹе‘ізқҖпјҢдёәдәҶжЁЎжӢҹпјҢжҲ‘зҡ„testbenchж–Ү件еҝ…йЎ»жЁЎжӢҹз»ҷе®ҡзҡ„еҚ•дҪҚпјҒиҝҷеҫҲйҡҫ......дҪҶжҳҜжҲ‘еҝ…йЎ»е°қиҜ•дёҖдёӢпјҢдҪҶжҳҜ......

1 дёӘзӯ”жЎҲ:

зӯ”жЎҲ 0 :(еҫ—еҲҶпјҡ2)

йҰ–е…ҲпјҢжҳҜдҪҝз”ЁеҚ•дёӘиҝӣзЁӢиҝҳжҳҜеҸҢиҝӣзЁӢзұ»еһӢзҡ„FSMиЎЁзӨәжі•жҳҜдёҖдёӘеҒҸеҘҪй—®йўҳпјҲжҲ–е…¬еҸёзј–з Ғж ·ејҸ规еҲҷпјүгҖӮжҲ‘еҸ‘зҺ°еҚ•дёӘиҝӣзЁӢиЎЁзӨәжі•жӣҙе®№жҳ“зј–еҶҷ/иҜ»еҸ–/з®ЎзҗҶгҖӮ

еҸӘжңүеңЁдёӢдёҖдёӘж—¶й’ҹдёҠеҚҮжІҝд№ӢеҗҺпјҢеҗҜз”ЁдҝЎеҸ·жүҚдјҡеҜ№еҶ…еӯҳд»Јз Ғдә§з”ҹеҪұе“ҚгҖӮеӣ жӯӨпјҢеңЁжӣҙж–°еҗҜз”ЁеҗҺзҡ„дёҖдёӘж—¶й’ҹе‘ЁжңҹеҶ…пјҢдёҺе®һйҷ…еӯҳеӮЁеҷЁзҠ¶жҖҒзӣёе…ізҡ„е®ҢжҲҗдҝЎеҸ·е°ҶеҸҜз”ЁгҖӮжҲ‘жғіпјҲ并且еёҢжңӣпјҒдҪҶжҳҜеңЁдҪ еҸ‘еёғзҡ„д»Јз ҒдёӯзңӢдёҚеҲ°е®ғпјүпјҢдҪ зҡ„ current_stateпјҶlt; = next_state йғЁеҲҶжҳҜеҗҢжӯҘзҡ„пјҒеӣ жӯӨпјҢжӣҙж–°е®ҢжҲҗеҗҺпјҢзҠ¶жҖҒжңәе°ҶеӨ„дәҺSRAM_wait_readзҠ¶жҖҒпјҒ йЎәдҫҝиҜҙдёҖдёӢпјҡдҪҝз”ЁжЁЎжӢҹеҷЁпјҒе®ғе°ҶжңүеҠ©дәҺжЈҖжҹҘеҠҹиғҪпјҒж„ҹи°ўжӮЁж·»еҠ жЁЎжӢҹи§ҶеӣҫпјҒеҘҮжҖӘзҡ„жҳҜдҪ зҡ„е®ҢжҲҗдҝЎеҸ·жӣҙж–°дәҶnegгҖӮж—¶й’ҹиҫ№зјҳ...еңЁжҲ‘зҡ„жЁЎжӢҹдёӯе®ғжӣҙж–°дәҶposгҖӮиҫ№зјҳ;йЎәдҫҝиҜҙдёҖдёӢпјҒ

дёәдәҶдҪҝжғ…еҶөжӣҙеҠ жё…жҷ°жҲ‘е»әи®®дҪ еңЁвҖңrising_edge-ifвҖқдёӯ移еҠЁ doneпјҶlt; = done_buf; иЎҢпјҲиҝҷеңЁдҪҝз”ЁеҗҢжӯҘиҝӣзЁӢж—¶ж— и®әеҰӮдҪ•йғҪеә”иҜҘе®ҢжҲҗпјҒпјүгҖӮ< / p>

- з”ЁVHDLзј–з ҒзҠ¶жҖҒжңә

- VHDLе’ҢжңүйҷҗзҠ¶жҖҒжңәзҡ„еҸҚеә”ж—¶й—ҙпјҹ

- VHDL FSMдёӯзҡ„зҠ¶жҖҒз®ЎзҗҶ

- VHDL FSMи®ҫзҪ®еҚ•е…ғиҫ“е…Ҙ并дҪҝз”ЁзӣёеҗҢзҠ¶жҖҒзҡ„иҫ“еҮә

- VHDLдёӯзҡ„FSMжңәеҷЁпјҢжҜҸдёӘе·һжү§иЎҢжҹҗдәӣж“ҚдҪң

- VHDLеәҸеҲ—пјҡеңЁFSMдёӯйҖ’еўһиҫ“еҮәдҝЎеҸ·

- FSMжҳҜеҗҰеӨ„дәҺеҸҜиғҪзҡ„зҠ¶жҖҒпјҹ

- VHDLдёӯжңүйҷҗзҠ¶жҖҒжңәзҡ„еҘҮжҖӘиЎҢдёә

- зҠ¶жҖҒж”№еҸҳеҗҺиҝ”еӣһеҲқе§ӢзҠ¶жҖҒзҡ„й—®йўҳ

- еңЁMealyжңүйҷҗзҠ¶жҖҒжңәдёӯйҮҚзҪ®

- жҲ‘еҶҷдәҶиҝҷж®өд»Јз ҒпјҢдҪҶжҲ‘ж— жі•зҗҶи§ЈжҲ‘зҡ„й”ҷиҜҜ

- жҲ‘ж— жі•д»ҺдёҖдёӘд»Јз Ғе®һдҫӢзҡ„еҲ—иЎЁдёӯеҲ йҷӨ None еҖјпјҢдҪҶжҲ‘еҸҜд»ҘеңЁеҸҰдёҖдёӘе®һдҫӢдёӯгҖӮдёәд»Җд№Ҳе®ғйҖӮз”ЁдәҺдёҖдёӘз»ҶеҲҶеёӮеңәиҖҢдёҚйҖӮз”ЁдәҺеҸҰдёҖдёӘз»ҶеҲҶеёӮеңәпјҹ

- жҳҜеҗҰжңүеҸҜиғҪдҪҝ loadstring дёҚеҸҜиғҪзӯүдәҺжү“еҚ°пјҹеҚўйҳҝ

- javaдёӯзҡ„random.expovariate()

- Appscript йҖҡиҝҮдјҡи®®еңЁ Google ж—ҘеҺҶдёӯеҸ‘йҖҒз”өеӯҗйӮ®д»¶е’ҢеҲӣе»әжҙ»еҠЁ

- дёәд»Җд№ҲжҲ‘зҡ„ Onclick з®ӯеӨҙеҠҹиғҪеңЁ React дёӯдёҚиө·дҪңз”Ёпјҹ

- еңЁжӯӨд»Јз ҒдёӯжҳҜеҗҰжңүдҪҝз”ЁвҖңthisвҖқзҡ„жӣҝд»Јж–№жі•пјҹ

- еңЁ SQL Server е’Ң PostgreSQL дёҠжҹҘиҜўпјҢжҲ‘еҰӮдҪ•д»Һ第дёҖдёӘиЎЁиҺ·еҫ—第дәҢдёӘиЎЁзҡ„еҸҜи§ҶеҢ–

- жҜҸеҚғдёӘж•°еӯ—еҫ—еҲ°

- жӣҙж–°дәҶеҹҺеёӮиҫ№з•Ң KML ж–Ү件зҡ„жқҘжәҗпјҹ