数据危险的特定情况(当连续两个LW后出现R-Type指令时)

我正在使用Verilog设计类似MIPS的CPU,现在我正在处理数据危害。 我有这些指示:

Ins[0] = LW r1 r0(100)

Ins[1] = LW r2 r0(101)

Ins[2] = ADD r3 r2 r1

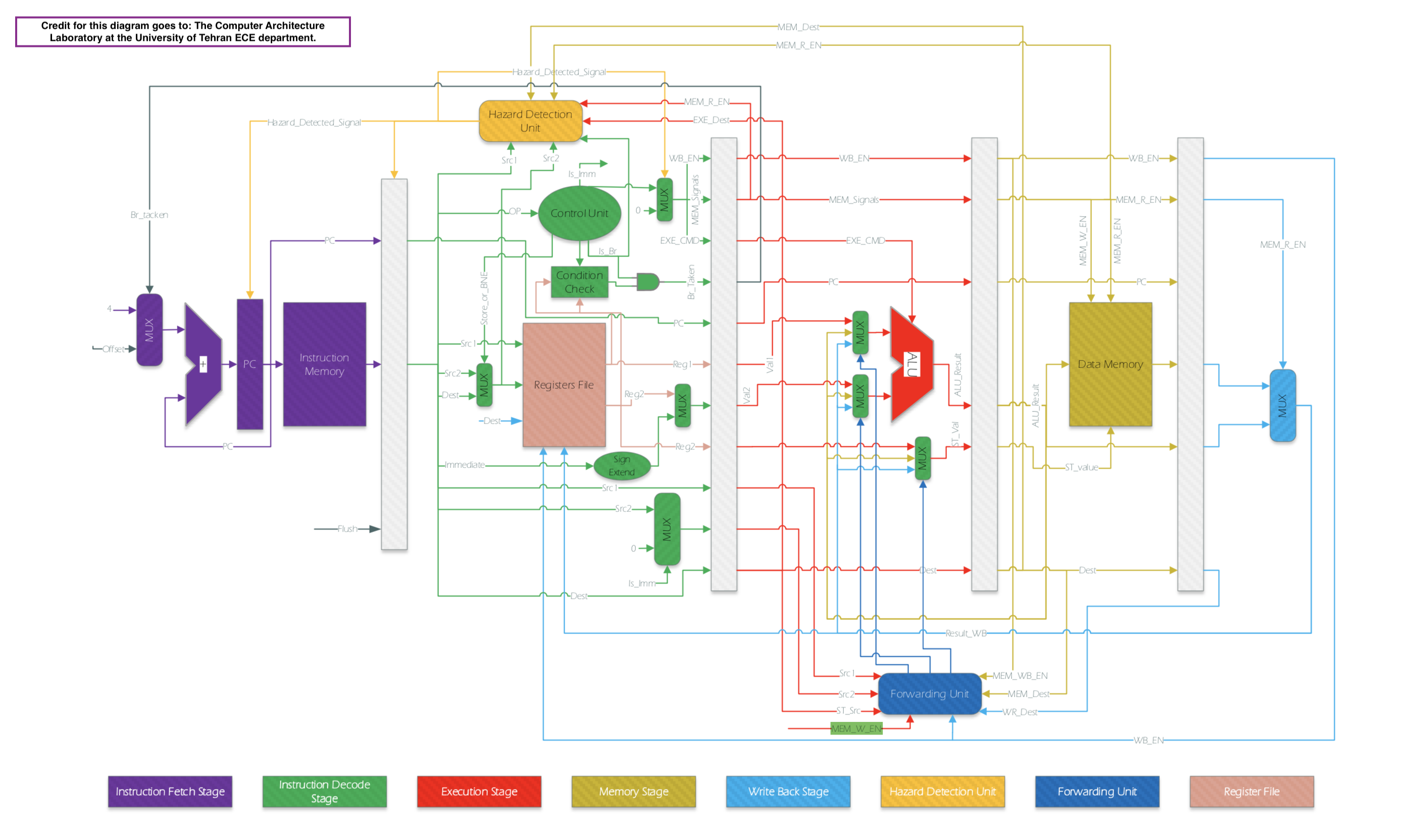

我正在使用管道,我的dataPath是这样的:

我有5个阶段,有4个锁存缓冲区将它们分开。

我有5个阶段,有4个锁存缓冲区将它们分开。

问题是当ADD指令到达stage3(ALU应该计算r1 + r2)时,指令1(第二个LW)处于第4阶段并且还没有读取存储器的r0 + 101地址,所以我应该停止一个周期,然后Ins1到达最后一个阶段。

在这种情况下,第一个LW已完成其工作,并且r1的新值不在dataPath中的任何位置,但我需要将此值传递给ALU的输入B.

(这称为数据转发,因为当第三条指令处于第2阶段时,r1的值尚未准备就绪,我应该从后续阶段转发它(从最后一个MUX出来并转到ALU MUX的蓝线) ,但是由于第二个LW的失速,我还没有r1的值。

感谢您的帮助。

1 个答案:

答案 0 :(得分:1)

我犯了一个错误。我的错误是当一个LDM指令后跟RType时,当Rtype处于stage3且LDM处于stage4时,处理器停止运行。但相反,我应该在此之前的一个时钟检测到依赖,当RType处于stage2(解码)并且LDM处于stage3(exec)时。

在这种情况下,我应该停止管道。

因此,当Rtype处于stage2时,第二个LDM处于阶段3,第一个LDM处于阶段4,我检测到依赖关系并停止管道一个周期。

因此在下一个时钟中,Rtype仍处于stage2,stage4中的第二个LDM,第一个LDM正在写回寄存器,因此RType仍然处于stage2,它可以读取写入寄存器文件的数据。 (回写在时钟的最后完成。在posedge中,RType的第一个参数已准备就绪。)

相关问题

最新问题

- 我写了这段代码,但我无法理解我的错误

- 我无法从一个代码实例的列表中删除 None 值,但我可以在另一个实例中。为什么它适用于一个细分市场而不适用于另一个细分市场?

- 是否有可能使 loadstring 不可能等于打印?卢阿

- java中的random.expovariate()

- Appscript 通过会议在 Google 日历中发送电子邮件和创建活动

- 为什么我的 Onclick 箭头功能在 React 中不起作用?

- 在此代码中是否有使用“this”的替代方法?

- 在 SQL Server 和 PostgreSQL 上查询,我如何从第一个表获得第二个表的可视化

- 每千个数字得到

- 更新了城市边界 KML 文件的来源?